в чем отличие асинхронных и синхронных триггеров

Асинхронные и синхронные триггеры

По способу ввода информации бывают асинхронные и синхронные триггеры.

Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе.

У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход.

Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации.

Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

Способы управления, в зависимости от параметра синхронного входа сигнала, используемых для записи информации, триггеры бывают:

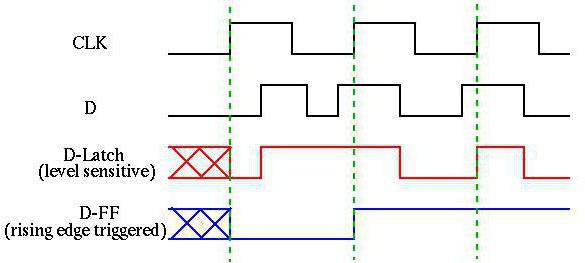

1) со статическим управлением записью (управление по уровню входного сигнала);

2) с динамическим управлением записью (по фронту или срезу);

3) двухступенчатое управление.

Способ управления со статическим управлением записью имеет недостаток – триггер в период действия синхронного импульса ведет себя подобно асинхронному. Срабатывает в момент, когда входной сигнал достигает порогового уровня, то есть продолжает действие тактового импульса. Смена сигнала на информационный вход вызывает новое срабатывание.

При динамическом управлении по фронту или по спаду тактового импульса триггер переключается только при переходе от 0 к 1, или от 1 к 0.

Возможность задержки момента опрокидывания триггера на время длительности тактового импульса позволяют по фронту производить считывание, а по срезу – запись информации.

Двухступенчатые триггеры содержат две ячейки памяти, запись информации в которые происходит последовательно в различные моменты времени. Эту структуру называют «ведущий-ведомый» или MS-структура (Master-Slave).

Первая ступень – промежуточная запись входной информации. Вторая ступень – последовательная запись и хранение.

Формирование нового состояния происходит за два такта.

Ввод информации в ведущую ступень происходит с приходом С1. Перезапись соответственно из ведущего в ведомый – с приходом С2, в это же время происходит обновление информации на Q или

Управлять можно и одним тактовым импульсом. Запись в ведущую по фронту 0-1, перезапись в ведомую – по фронту 1-0.

Динамические двухступенчатые триггеры называют флип-флоп. Статические – лэт.

Асинхронные и синхронные триггеры

Независимо от способа организации логических связей триггеры различаются по способу ввода информации и по этому признаку могут быть асинхронными и синхронными.

У асинхронных триггеров имеются только информационные (логические) входы. Асинхронные триггеры отличает свойство срабатывать непосредственно за изменением сигналов на входах, не считая времени задержки в элементах, образующих триггер.

Синхронные триггеры кроме информационных входов имеют также вход подачи тактового сигнала «С». Синхронный триггер состоит из КС (комбинационных схем) и ЭП (элементов памяти), в качестве которых используются синхронные элементы задержки D информационных сигналов Q + на один период тактового сигнала «С». Из этого следует, что различие синхронных и асинхронных потенциальных триггеров заключается лишь в использовании в различных по функциям ЭП. В синхронных ЭП тактовый сигнал оказывает на них импульсное воздействие в моменты изменения с 0 на 1 (или с 1 на 0), а изменения информационных сигналов Q

Тактовый сигнал С выполняет функцию временного селектирования информационных сигналов ЭП Q + r в моменты времени tД, поэтому требуется, чтобы значения информационных сигналов были истинными в эти моменты времени.

У синхронных триггеров смены сигналов на входах еще не достаточно для срабатывания. Необходим дополнительный командный импульс, который подается на синхронный, или так называемый тактирующий вход.

Основной недостаток асинхронных триггеров, ограничивающий их использование в быстродействующих схемах, – незащищенность перед опасными состязаниями сигналов. Явление состязаний или, как его еще называют, гонок, состоит в том, что сигналы, поступают на разные информационные входы триггера, пройдя различное число элементов. Вследствие задержек распространения между сигналами возможны временные сдвиги. Состязания сигналов могут оказаться причиной ложных срабатываний триггеров. Тактированием этот недостаток можно устранить.

Синхронные триггеры по сравнению с асинхронными обладают более высокой помехоустойчивостью. Опрокидывание синхронных триггеров происходит только при участии тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входные сигналы, ровно как и помехи различного происхождения, триггер не реагирует. В асинхронном же управлении опрокидывание может произойти как от полезного сигнала, так и от помехи.

Асинхронный триггер по большей части используют в качестве ключей, прерывателей, делителей частоты. В вычислительной и цифровой технике, связанной с обработкой информации, везде используют синхронные системы.

Способы управления триггерами

В зависимости от того, какой параметр входных сигналов используют для записи информации, триггеры подразделяются на три категории: со статическим управлением (управление по уровню входного сигнала), динамическим управлением (управление по фронту или срезу) и двухступенчатые триггеры. Для асинхронных триггеров в качестве управляющих служат сигналы на информационных входах. Применительно к синхронным триггерам управляющим сигналом служит тактовый импульс, так как считается, что к его приходу смена сигналов на информационных входах уже завершилась.

Рис. 58. Момент срабатывания триггеров с разными способами управления: а) статическим; б) прямым динамическим (по фронту 0,1); в) инверсным динамическим (по срезу 1,0);

t – время, в течение которого может происходить обратный переброс

Специфика синхронных триггеров со статическим управлением такова, что в продолжение времени действия тактового сигнала смена сигналов на информационных входах вызовет новое срабатывание. Другими словами, синхронные триггеры со статическим управлением при активном состоянии тактового входа ведут себя подобно асинхронным.

От этого свободны триггеры с динамическим двухступенчатым управлением.

максимальная входная частота

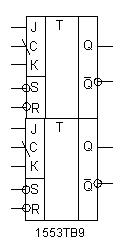

JK-триггеры

Этот тип триггеров (рис. 59) не имеет неопределенных состояний. Функциональная особенность JK-триггера состоит в том, что при всех входных комбинациях, кроме одной J n = K n = 1, они действуют подобно RS-триггеру, причем вход J играет роль входа S, а К-вход соответствует R-входу. При входной комбинации J n = K n = 1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам. Их универсальность имеет двойственный характер. Во-первых, эти триггеры могут быть применены в регистрах, счетчиках, делителях частоты и других узлах, и, во-вторых, путем определенного соединения выводов они обращаются в триггеры других типов.

При входных сигналах J = H(0) и K = H(0) состояние выходов не меняется, оно сохраняется таким, каким было в момент установки. Напряжение низкого уровня (Н) на одном входе элемента ТТЛ отменяет прохождение от других его входов и удерживает выходной сигнал на высоком уровне. Когда через входы

J и K в момент времени установлены противоположные уровни, то в последующий момент выходы JK-триггера устанавливаются в такие же состояния, как и RS-триггер.

При подаче на входы J и K одновременно напряжений высокого уровня (входы можно просто соединить) триггер перебрасывается, переходит в состояние, противоположное предыдущему. Если было Qn = B(1),

Для надежной работы триггерных ячеек в многоразрядных устройствах управления (счетчиках, регистрах) предназначены двухступенчатые триггеры (master – slave).

С учетом тактового сигнала С функция перехода JK-триггера описывается выражением

Q + =

Рис. 60. Карта Карно для функции перехода JK-триггера

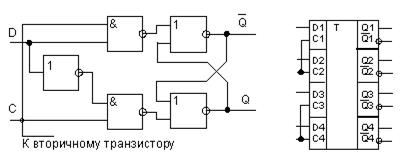

D-триггеры

Для D-триггера требуется всего четыре внешних вывода: вход данных D, тактовый вход С и два выхода Q и

На вход D подается напряжение уровнем «1» или «0». Если в последующий момент времени придет положительный перепад тактового импульса состояния, на выходах Qn + 1 и

В заключение рассмотрим схемы взаимного преобразования триггеров. На рис. 62, а – в показаны схемы делителей частоты на RST-, D- и JK-триггерах соответственно. Триггер D возможно преобразовать в Т (делитель на 2), снабдив делитель дополнительным входом разрешения ЕI (рис. 62, г). В режиме

D-триггера можно использовать JK- и RST-триггеры (рис. 62, е). Из RST-триггера можно получить JK-триггер по схеме (рис. 62, ж).

Рис. 62. Схемы взаимного преобразования триггеров

Счетчики

Счетчиком называется устройство, совокупность сигналов на входе которого в определенном коде отображает число импульсов, поступивших на его вход. Счетчик – последовательное устройство, предназначенное для счета входных импульсов и фиксации их числа в двоичном коде.

Счетчики строятся на основе N однотипных связанных между собой (последовательно) разрядных схем, каждая из которых в общем случае состоит из Т-триггеров (счетных делителей на два) и некоторой комбинационной схемы, предназначенной для формирования сигналов управления триггерами.

В цифровых схемах счетчики могут выполнять следующие микрооперации над кодовыми словами:

1) установка в исходное состояние (запись нулевого кода);

2) запись входной информации в параллельной форме;

3) хранение информации;

4) выдача хранимой информации в параллельной форме;

5) инкремент – увеличение хранящегося кодового слова на единицу (Up);

6) декремент – уменьшение хранящегося кодового слова на единицу (Down).

Основные параметры и классификация счетчиков.Основным статическим параметром счетчика является модуль счета М, который характеризуется максимальным числом импульсов, после прихода которого счетчик устанавливается в исходное состояние. Каждый триггер имеет два устойчивых состояния, поэтому количество комбинаций выходных сигналов, снимаемых с выходов всех триггеров, а соответственно, и максимальное число подсчитанных импульсов N равно

где m – количество последовательно включенных триггеров.

Каждый из триггеров такой цепочки называют разрядом счетчика, поэтому если, например, m – 4, то счетчик четырехразрядный. Максимальное число, которое может подсчитать счетчик Nmax, называется коэффициентом, или модулем счета КСЧ (КСЧ = Nmax). Если количество входных импульсов Nmax больше КСЧ, то происходит переполнение счетчика. При этом он возвращается в исходное состояние и цикл снова повторяется.

Такие счетчики выполняют функцию деления частоты и называются счетчиками – делителями.

Цифровые счетчики классифицируются следующим образом.

По коэффициенту (модулю) счета: двоичные (бинарные); двоично-десятичные (декадные) или с другим коэффициентом счета; с произвольным; постоянным модулем; с переменным модулем.

По направлению счета: суммирующие; вычитающие; реверсивные.

По способу организации внутренних связей: с последовательным переносом; с параллельным переносом; комбинированным переносом; кольцевые; счетчики Джонсона. Удобно использовать терминологию: суммирующие счетчики (UP – counter), вычитающий счетчик (Down – counter), реверсивный (UP – down – counter).

Синхронные и асинхронные триггеры: в чем разница?

Синхронные устройства имеют только логические (или по-другому – информационные) входы. Асинхронные механизмы срабатывают сразу, как только получили сигнал. Они не ждут, пока пройдёт временная задержка в тех элементах, которые образуют триггер. Асинхронный D-триггер не работает как устройство в обычном понимании. Благодаря этому он имеет один несомненный плюс: всегда, когда подаётся сигнал на вход, этот логический элемент сразу меняет значение выхода, а не ждёт определённой тактовой частоты. Для тех, кто умеет создавать близкие к идеальным схемы, триггеры будут весьма полезны.

Синхронные имеют не только информационные входы, у них также есть отдельный вход для подачи тактового сигнала. И именно к ним относится D-триггер. Он состоит из комбинационных схем (КС) и элементов памяти (ЭП). Из-за того что при наличии тактового сигнала вся работа ориентируется на один такт, триггеры и разделили на синхронные и асинхронные устройства. Но конструктивная разница на этом не исчерпывается. Так, именно благодаря тактовому сигналу, его воздействию, можно полностью исключать из внимания переходные процессы, что позволяет, в свою очередь, облегчить работу с электроникой. Именно поэтому синхронный D-триггер является более популярным и используемым на практике. Даже пример, который был приведён в начале статьи, подразумевал его использование.

Регистр — устройство, используемое для хранения n-разрядных двоичных данных и выполнения преобразований над ними.

Регистр представляет собой упорядоченный набор триггеров, обычно D-, число n которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное [ уточнить ] цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Основой построения регистров являются: D-триггеры, RS-триггеры, JK-триггеры.

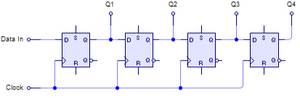

4-х разрядный сдвиговый регистр, преобразователь последовательного кода в параллельный и обратно

Параллельные и последовательные регистры

Всем доброго времени суток! В прошлом посте я писал про триггеры, а сегодня практически продолжение этой темы – регистры. Почему продолжение? Потому что регистры (англ. Register) представляют собой несколько триггеров соединённых между собой различными способами.

Вообще регистров бывает два основных вида:

В обозначениях микросхем для регистров выделено суффикс ИР, например, К555ИР9, К555ИР27, К1533ИР35.

Параллельный регистр

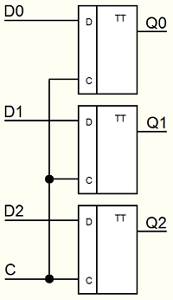

Схема соединения триггеров в параллельном регистре

В данном типе регистров триггеры соединены параллельно, то есть каждый внутренний триггер имеет свой вход D и свой выход Q, которые не зависят от других триггеров, а также вход С, который называется тактовым входом и для всех входящих в регистр триггеров он является общим. Параллельные регистры бывают двух типов:

Наибольшее распространение получили тактируемые параллельные регистры.

Механическое удерживание земляных масс: Механическое удерживание земляных масс на склоне обеспечивают контрфорсными сооружениями различных конструкций.

Асинхронные и синхронные триггеры

По способу ввода информации бывают асинхронные и синхронные триггеры.

Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе.

У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход.

Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации.

Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

Способы управления, в зависимости от параметра синхронного входа сигнала, используемых для записи информации, триггеры бывают:

1) со статическим управлением записью (управление по уровню входного сигнала);

2) с динамическим управлением записью (по фронту или срезу);

3) двухступенчатое управление.

Способ управления со статическим управлением записью имеет недостаток – триггер в период действия синхронного импульса ведет себя подобно асинхронному. Срабатывает в момент, когда входной сигнал достигает порогового уровня, то есть продолжает действие тактового импульса. Смена сигнала на информационный вход вызывает новое срабатывание.

При динамическом управлении по фронту или по спаду тактового импульса триггер переключается только при переходе от 0 к 1, или от 1 к 0.

Возможность задержки момента опрокидывания триггера на время длительности тактового импульса позволяют по фронту производить считывание, а по срезу – запись информации.

Двухступенчатые триггеры содержат две ячейки памяти, запись информации в которые происходит последовательно в различные моменты времени. Эту структуру называют «ведущий-ведомый» или MS-структура (Master-Slave).

Первая ступень – промежуточная запись входной информации. Вторая ступень – последовательная запись и хранение.

Формирование нового состояния происходит за два такта.

Ввод информации в ведущую ступень происходит с приходом С1. Перезапись соответственно из ведущего в ведомый – с приходом С2, в это же время происходит обновление информации на Q или

Управлять можно и одним тактовым импульсом. Запись в ведущую по фронту 0-1, перезапись в ведомую – по фронту 1-0.

Динамические двухступенчатые триггеры называют флип-флоп. Статические – лэт.

Асинхронные RS-триггеры.

|  | V |  |

| |||

| Х | |||

| Х | Х | Z |

X – не имеет значения

Z – высокоимпедансное значение выхода (выход отключен от обеих шин источника питания и выходных клемм)

Отсутствие запрещенного состояния обусловлено тем, что не введены выводы

Синхронные RS-триггеры.

При С = 0 на выходах DD2 и DD1 логическая «1» и RS-триггер на DD3 и DD4 находится в состоянии хранения информации (и не реагирует на изменение R и S). При С = 1, информация на управляющих входах RS-триггера зависит от состояния входа R и S, проинвертированных DD2 и DD1. Входы Sa¯ и Ra¯ предназначены для асинхронной установки триггера в заданное состояние.

Двухступенчатые RS-триггеры.

При высоком уровне на входе С происходит запись в ведущий RS-триггер на DD1 – DD4. Ведомый триггер на DD6 – DD9 блокирован низким уровнем с выходом DD5. При низком уровне на входе С блокируется ведущий триггер (переходит в состояние хранения информации). Высокий уровень с выхода DD5 разрешает перезапись с выхода ведущего на вход ведомого.

JK-триггеры

JK-триггеры не имеют неопределенных состояний. При всех входных комбинациях, кроме J = K = 1, они действуют подобно RS-триггеру. Причем J играет роль S, а К=R.

При J=K=1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам (регистры, счетчики, делители), но кроме того, путем определенных соединений выводов, легко преобразуются в триггеры других типов.

По схеме JK-триггеры отличаются от RS-триггеров наличием обратной связи с выхода на вход, поэтому состояние JK-триггера зависит не только от сигналов на входах J и K, но и от логической связи с ними сигнала с выходов Q и Q¯. Элементы временной задержки играют роль стабилизированного состояния триггера и на его функциональные свойства не влияют. Назначение – создание временного сдвига между моментом ввода входной информации J n Q n ¯ или K n Q n и начала выхода Q n +1 и Q n +1 ¯.

Без этих цепей во время действия комбинации J n = K n = 1 началась бы генерация для предотвращения которой задержка должна быть превыше длительности тактирующих импульсов.

Триггер организован по принципу ведущий-ведомый и имеет по 3 входа J и K, связанных операцией &, синхронный вход С, а также асинхронные входы

У ТВ6 отсутствует вход

RS-триггер. ( в скобках R-триггер)

D–триггеры серии ТМ7 со статическим управлением внутренними, объединенными попарно, синхронизирующими входами используются в качестве четырехразрядного регистра хранения информации с попарным тактированием разряда, а также в качестве буферной памяти и элемента задержки.

У ТМ5 отсутствует инверсный выход.

ТМ8 – с динамическим управлением.

У DV-триггера разрешающий уровень появляется до сигнала. Если V = 1, то триггер функционирует как D-триггер, при V = 0 – переходит в режим хранения информации. Это расширяет функцию D-триггера, который не может хранить информацию более одного такта.

T-триггер – счетный триггер, который имеет один информационный вход и меняет свое состояние всякий раз, когда меняет свое значение входной сигнал. В зависимости от того, фронт или срез используется для управления, считается, что триггер имеет прямой или инверсный вход. Единственный вид триггера, состояние которого определяется состоянием в предыдущем такте, а не от входной информации. Выполняет операцию сложения по модулю 2. Легко получается из D- или JK-триггера.

TV-триггер Сихронный TV-триггер

Несимметричные триггеры (Триггеры Шмита).

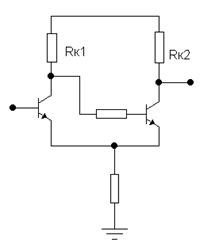

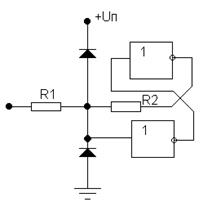

Триггер Шмитта на транзисторах. Нужен для ускорения сигнала.

| КМОП | ТТЛ | |

| R1 | (10  50)k 50)k | (200  500)k 500)k |

| R2 | (0,1  1)k 1)k | (2,2  3,3)k 3,3)k |

Счетчики импульсов. Двоичные счетчики и счетчики с произвольным коэффициентом счета. Принцип действия, структурные и принципиальные схемы, временные диаграммы работы счетчиков, их основные параметры. Разновидности счетчиков, особенности использования счетчиков при создании цифровых систем управления.

Счетчиком называется устройство, сигналы на выходе которого в определенном коде отображают число импульсов, поступивших на счетный вход. Счетчик, образованный цепочкой из m триггеров может подсчитать в двоичном коде

Информация может сниматься с прямых и инверсных выходов триггеров. Когда число входных импульсов

Коэффициент счета называют коэффициентом деления, следовательно каждый счетчик может использоваться как делитель частоты.

Основные параметры: емкость и быстродействие. Емкость численно равна коэффициенту счета и характеризует число импульсов, доступных счету за 1 цикл. Быстродействие определяется двумя параметрами: разрешающей способностью и временем установления.

Под разрешающей способностью подразумевают минимальное время между двумя сигналами, при которых еще не возникают сбои в работе tразр.сч.

Время установления кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое состояние.

Счетчики классифицируются следующим образом:

· с произвольным фиксированным модулем счета

· с переменным модулем

2) по направлению счета:

3) по способу организации внутренних связей

· с последовательным переносом (асинхронные)

· с параллельным переносом (синхронные)

· с комбинированным переносом

Классификационные признаки независимы и могут встречаться в разных комбинациях.

Число, записанное в счетчик, определяется по формуле:

где m – номер триггера,

Q – может принимать значение «1» и «0»,

Введением дополнительных логических связей (обратных и прямых) счетчики могут быть обращены в недвоичные, для которых

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которых импульсы, подлежащие счету, поступают на вход 1-го триггера, а сигнал переноса передается последовательно от одного разряда к другому.

Достоинства: простота схемы и увеличение разрядности.

Недостатки: низкое быстродействие из-за последовательного принципа работы.

Счетчики с параллельным переносом.

У них счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующему только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, а задержка переключения всего счетчика равна задержке одно триггера.

В счетчике с параллельно-последовательным переносомтриггеры соединены в группы так, что отдельные группы образуют счетчики с параллельным переносом внутри группы, а группы соединяются в счетчик с последовательным переносом. Общий коэффициент счета равен произведению коэффициентов счета всех групп.