в чем суть каскадирования мультиплексоров

Наращивание мультиплексоров

ИМС мультиплексоров имеют ограниченное число информационных входов (каналов передачи информации). Если необходимое число каналов превышает возможности одной ИМС, мультиплексоры наращивают в систему. В этом отношении мультиплексоры принципиально не отличаются от дешифраторов. Каскадирование ИМС мультиплексоров, как и дешифраторов, возможно по пирамидальной схеме и путём последовательного соединения их разрешаемых входов через внешние логические элементы или непосредственно друг с другом. Адресные входы наращиваемых мультиплексоров делятся, как и в случае наращивания дешифраторов, на старшие (СРА) и младшие (МРА) разряды адреса. СРА выбирают кристаллы (ИМС) адресуемого мультиплексора. Младшие разряды, поступая на адресные входы всех мультиплексоров, выбирают только один, соответствующий

канал передачи информации выбранного СРА кристалла, так как функционирование остальных кристаллов запрещено (табл. 3.6.).

Выходы каскадируемых мультиплексоров объединяются следующим образом: неинвертирующие выходы через логические элементы ИЛИ; инвертирующие выходы через ЛЭ И – НЕ, которые реализуют функцию ИЛИ в отрицательной логике; выходы с третьим высокоимпедансным состоянием или открытым коллектором

объединяются согласно правилам монтажной логики. Рассмотрим несколько примеров каскадирования ТТЛ – мультиплексоров. На рис. 3.6 представлена пирамидальная схема мультиплексора 64→1, в которой двоичный код МРА подается параллельно на адресные входы всех мультиплексоров DD2…DD9. Однако с выходом Y соединяется лишь один соответствующий вход мультиплексора, выбранного кодом СРА через дешифратор DD1.

Рис. 3.6. Мультиплексор 64→1 с стробирующим входом DD1 – K5554D4; DD2…DD9 – K555KП7; DD10 – K555ЛА2

рассмотренной схемы возможна

стробирующих входов Е.

мультиплексоров без входов стробирования возможно по

Рис. 3.7. Мультиплексор 64→1 (без входов стробирования) DD1…DD9 – 155KП5

Схема мультиплексора 16→1 (рис. 3.8) иллюстрирует другой способ наращивания мультиплексоров путём последовательного

соединения входов стробирования через инвертор. Двоичный код,

подаваемый на адресные входы

входов 0…15 будет соединён через логический элемент И-НЕ с выходом Y.

Рис. 3.8. Мультиплексор 16→1 на ИМС DD1,DD2 – K555KП7; DD3 – K555ЛА3

Наращивание КМОП – мультиплексоров можно проводить аналогично рассмотренным выше схемам (рис. 3.6…3.8). Однако при этом следует учитывать некоторые особенности их схемотехники. Так, дешифратор К564ИД1 имеет выходной сигнал с активным уровнем, равным лог. “1”, а ИМС КМОП – мультиплексоров функционируют при стробирующем сигнале, равном уровню лог. “0” (Е=0). Следовательно, при каскадировании КМОП – мультиплексоров по схеме рис 3.6 выходы дешифратора следует соединять с соответствующими входами стробирования мультиплексоров через инверторы, и их выходы по правилам монтажной логики (рис 3.9).

информационных выходах 0…7 дешифратора устанавливаются

уровни лог. “0”, а на выходах инверторов уровни лог. “1”, поэтому работа всех ИМС DD4…DD11 запрещена, все каналы, передающие информацию, закрыты.

Рис. 3.9. Мультиплексор 64:1 со стробирующим входом

DD1 – K564ИD1, DD2,DD3 K564ЛН2; DD4…DD11 K564КП2

Если в этой схеме (рис. 3.9) заменить ИМС 564КП2 на

К564КП1, то получим двойной 32канальный мультиплексор (рис.

Если необходимо построить один мультиплексор на двойных мультиплексорах на большее число входов, то можно использовать схему, приведённую на рис 3.11.

На рис. 3.12 приведен пример построения мультиплексора

8→1 на ИМС К564КП1. В этой схеме по сравнению с рисунком 3.11

вторая ступень мультиплексирования выполнена на двунаправленном ключе К564КТ3.

Рис. 3.10. Мультиплексор 2 × (32→1) DD1 – K564ИD1, DD2,DD3 K564ЛН2; DD4…DD11 K564КП1

При наращивании КМОП – мультиплексоров возможно,

аналогично рис. 3.8, последовательное соединение их входов

стробирования. На рис. 3.13 приведена схема двойного шестнадцатиканального мультиплексора, построенного по этому принципу.

Рис. 3.11. Мультиплексор 16→1 DD1, DD2, DD3 K564КП1

Рис. 3.12. Мультиплексор 8→1 DD1 K564КП1, DD2 K564ПН2, DD3 K564КТ3

Рис. 3.13. Мультиплексор 2× (8→1) DD1, DD2 K564КП1, DD3 K564ЛН2

Рассмотренные выше схемы наращивания КМОП –

мультиплексоров сохраняют все их свойства и могут передавать как

цифровую, так и аналоговую информацию в двух направлениях: от входа к выходу и от выхода к входу, то есть их можно использовать как мультиплексоры – демультиплексоры.

Материал взят из книги Цифровые интегральные микросхемы (Асмолов Г.И.)

Каскадирование мультиплексоров

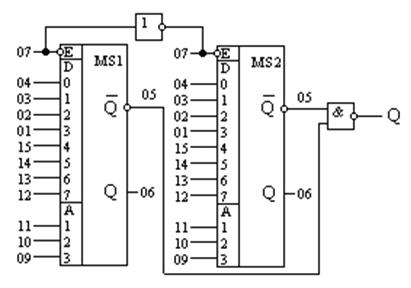

Один из способов увеличения числа коммутируемых каналов в схемах, построенных на мультиплексорах со стробированием, показан на (рис. 4.5). Таким способом на основе 8-канального мультиплексора можно построить любой мультиплексор 8 × 2 n à 1. На данном примере подробно показано, как аналитическое описание функционирования ИС дает возможность безошибочно проектировать достаточно сложные (по числу ИС) схемы, не указывая даже конкретные ее параметры (в данном случае значение n).

Рис. 4.5 Пример каскадирования мультиплексоров

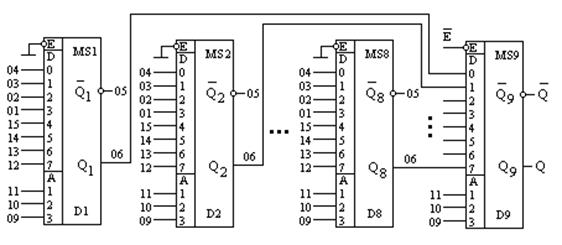

Второй способ увеличения числа коммутируемых каналов в схемах, построенных на мультиплексорах со стробированием, показан на (рис. 4.6).

Рис. 4.6 Пример каскадирования мультиплексоров с использованием дополнительного мультиплексора

Вместо ЛЭ «И-НЕ» используется дополнительный мультиплексор D9, производящий выбор одного из мультиплексоров D1 – D8, с помощью адресных сигналов х6, х5, х4. Данная схема выполняет функцию:

Вход

Мультиплексоры и демультиплексоры

Мультиплексоры и демультиплексоры

Цель работы: практическое освоение принципов построения мультиплексоров и демультиплексоров и экспериментальное их исследование на лабораторном стенде.

Мультиплексор – это комбинационная многовходовая схема с одним выходом. Входы мультиплексора подразделяются на информационные Д0, Д1, …, Дn-1 и управляющие (адресные) А0, А1, …, Аk-1. Обычно 2k = n, где k и n – число адресных и информационных входов соответственно. Двоичный код, поступающий на адресные входы, определяет (выбирает) один из информационных входов, значение переменной с которого передается на выход y, т. е. мультиплексор реализует функцию:

Таблица функционирования, описывающая работу мультиплексора, имеющего, например, n = 4 информационных (Д0, Д1, Д2, Д3) и k = 2 адресных (А0, А1) входов, представлена в табл. 1.

Вариант схемной реализации мультиплексора “4-1” (“четыре в один”, т. е. коммутирующего данные от одного из четырех входов на единственный выход) и его условное графическое изображение представлены на рис. 1.

Здесь мультиплексор построен как совокупность двухвходовых конъюкторов данных (их число равно числу информационных входов), управляемых выходными сигналами дешифратора, дешифрирующего двоичный адресный код. Выходы конъюкторов объединены схемой ИЛИ.

Рис. 1. Схема мультиплексора с дешифратором (а)

и и его условное графическоеизображение

В интегральном исполнении применяется более простая схема, в которой конъюкторы дешифратора одновременно выполняют и функцию конъюкторов данных. Работа мультиплексора при этом описывается соотношением

Из (2) следует, что при любом значении адресного кода все слагаемые, кроме одного равны нулю. Ненулевое слагаемое равно Дi, где i – значение текущего адресного кода.

Мультиплексоры 4-1, 8-1, 16-1 выпускаются в составе многих серий цифровых интегральных схем и имеют буквенный код КП. Например, К555КП1 – мультиплексор 2-1 (в данном корпусе размещаются четыре мультиплексора), К555КП12 – мультиплексор 4-1 (в одном корпусе размещаются два мультиплексора) и т. д.

В тех случаях, когда функциональные возможности ИС мультиплексоров не удовлетворяют разработчиков по числу информационных входов, прибегают к их каскадированию с целью наращивания числа входов до требуемого значения. Наиболее универсальный способ наращивания размерности мультиплексора состоит в построении пирамидальной структуры, состоящей из нескольких мультиплексоров. При этом первый ярус схемы представляет собой столбец, содержащий столько мультиплексоров, сколько необходимо для получения нужного числа информационных входов. Все мультиплексоры этого столбца коммутируются одним и тем же адресным кодом, составленным из соответствующего числа младших разрядов общего адресного кода. Старшие разряды адресного кода используются во втором ярусе, мультиплексор которого обеспечивает поочередную работу мультиплексоров первого яруса на общий выход.

Демультиплексор – схема, выполняющая функцию, обратную функции мультиплексора, т. е. это комбинационная схема, имеющая один информационный вход (Д), n информационных выходов (у0, у1, …, уn-1) и k управляющих (адресных) входов (А0, А1, …, Аk-1). Обычно, также как и мультиплексоров, 2k = n. Двоичный код, поступающий на адресные входы, определяет один из n выходов, на который передается значение переменной с информационного входа (Д), т. е. демультиплексор реализует следующие функции:

Таблица функционирования демультиплексора, имеющего n = 4 информационных выходов (у0, у1, у2, у3) и k = 2 адресных входов (А0, А1), представлена в табл. 2.

Уравнения, описывающие работу демультиплексора:

Рис. 4. Схема демультиплексора «1-4» (а)

и его условное изображение (б)

1.3 Применение мультиплексоров и демультиплексоров

1.3.1. Термином “мультиплексирование” называют процесс передачи данных от нескольких источников по общему каналу, а устройство, осуществляющее на передающей стороне операцию сведения данных в один канал, принято называть мультиплексором. Подобное устройство способно осуществлять временное разделение сигналов, поступающих от нескольких источников, и передавать их в канал (линию) связи друг за другом в соответствии со сменой кодов на своих адресных входах.

На приемной стороне обычно требуется выполнить обратную операцию – демультиплексирование, т. е. распределение порций данных, поступивших по каналу связи в последовательные моменты времени, по своим приемникам. Эту операцию выполняет демультиплексор. Совместное использование мультиплексора и демультиплексора для передачи данных от n источников к n приемникам по общей линии иллюстрирует рис. 5. (В общем случае число источников данных не равно числу приемников).

1.3.2. Если в схеме (рис. 5) n различных источников и приемников заменить n-разрядными источником и приемником, например, регистрами RGист. и RGпр. (изображены пунктирными линиями), то схема может быть использована для преобразования n-разрядного параллельного кода на передающей стороне в последовательный код (с помощью мультиплексора) и последовательного кода в параллельный на приемной стороне (с помощью демультиплексора). При подобном применении мультиплексора и демультиплексора в качестве их адресных кодов используются выходные сигналы двоичного счетчика, последовательно формирующего на своих выходах двоичные коды чисел от 0 до n-1.

1.3.3. Мультиплексор можно использовать в качестве универсального логического элемента для реализации любой логической функции от числа аргументов, равного числу адресных входов мультиплексора. Покажем это на примере логической функции, заданной своей таблицей истинности (табл. 3).

2. Задание на лабораторную работу

2.1. Используя ЛЭ, установленные на лабораторном стенде, спроектировать схему мультиплексора и исследовать его работу (снять таблицу истинности). Размерность мультиплексора и тип (базис) ЛЭ задаются табл. 4.

Каскадное соединение мультиплексоров

Рассмотрим пример. Необходимо синтезировать схему мультиплексора, обеспечивающего выбор «1 из 16» на базе мультиплексоров «1 из 4».

увеличить изображение

Рис. 6.3.Каскадное включение мульти-плексоров «1 из 16» на базе «1 из 4»

Схему каскада той же разрядности можно реализовать на базе мультиплексоров с большей разрядностью, например, «1 из 8» (рис. 6.4). Для наглядности на рис. 6.4 указан тот же пример подачи информации на входы каскада: А3А2А1А0=11102= 1410.

увеличить изображение

Рис. 6.4.Каскадное включение мультиплексоров «1 из 16» на базе «1 из 8»

Закономерность построения каскада мультиплексоров аналогична каскадированию дешифраторов. Но построение начинается со входной (а не выходной, как у дешифраторов) очереди каскада. На адресные линии всех мультиплексоров этой очереди подключается соответствующее разрядности базового мультиплексора количество линий адреса. Принципиальное отличие каскада мультиплексоров состоит в том, что все входящие в него мультиплексоры работают одновременно (разрешающий сигнал Е подается на все мультиплексоры сразу).

увеличить изображение

Рис. 6.5.Каскад мультиплексоров на 16 входов на базе «1 из 2»

увеличить изображение

Рис. 6.6.Каскад мультиплексоров на 16 входов на базе «1 из 8»

При синтезе каскада мультиплексоров рекомендуется придерживаться следующей последовательности действий:

Цифровая электроника

Мультиплексоры и демультиплексоры

Мультиплексор — комбинационное цифровое устройство, которое обеспечивает передачу на единственный выход F одного из нескольких входных сигналов Dj в соответствии с поступающим адресным кодом A i . При наличии n адресных входов можно реализовать M=2 n комбинаций адресных сигналов, каждая из которых обеспечивает выбор одного из M входов. Чаще всего используются мультиплексоры «из 4 в 1» (n=2, M=4), «из 8 в 1» (n=3, M=8), «из 16 в 1» (n=4, M=16). Правило работы мультиплексора «из 4 в 1» можно задать таблицей истинности:

Логическое выражение для выходной функции, заданной таблицей, можно записать в виде

Рис. 4.13.Структура и УГО мультиплексора «из 4 в 1».

Рис. 4.14.Пирамидальное каскадирование мультиплексоров.

Мультиплексоры первого уровня управляются адресными сигналами А0 и А1, а мультиплексоры второго – адресными сигналами А2 и А3. Каждый из мультиплексоров первого уровня выбирает один из четырех разрядов Dj. Первый мультиплексор выбирает один из разрядов D0 – D3, второй мультиплексор – один из разрядов D4 – D7 и т.д. Выходы с мультиплексоров первого уровня объединяются в мультиплексоре второго уровня, который осуществляет окончательную коммутацию и формирование выходного сигнала F.

Мультиплексор можно реализовать, используя дешифратор и схемы И и ИЛИ ( рис. 4.15 ). Дешифратор формирует логическую единицу на одном из выходов согласно входному двоичному коду. Сигналы с выходов дешифратора являются стробирующими, т.е. разрешающими сигналами для схемы совпадения единиц, реализованной на двухвходовых элементах И. Логическая единица будет формироваться на выходе только того элемента И, на один вход которого подается единица с выхода дешифратора и на второй вход – единица с соответствующего входа Dj. Для объединения выходов всех элементов И в один выход F, служит элемент ИЛИ. На его выходе формируется логическая единица, если таковая присутствует на опрашиваемом в данный момент входе Dj.

Рис. 4.15. Реализация мультиплексора на базе дешифратора.

Демультиплексор выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Ai направляет информацию с единственного входа D на один из M выходов Fj. При этом на остальных выходах будут логические нули (единицы). Принцип работы демультиплексора «из 1 в 4» иллюстрируется таблицей истинности: