в чем разница нанометров процессора

7 нм техпроцесс в чипах: Померяемся нанометрами? РАЗБОР

Snapdragon 865, Apple A13 bionic, новый Ryzen от AMD. Отовсюду нам кричат про 7-нанометровый техпроцесс в смартфонах и ПК! Чем это отличается от знакомых 10 и 14 нанометров? Как влияет на батарейку, производительность, нагрев? А тут еще и Samsung с Google анонсируют процессоры на 5 нм, кто-то уже вообще говорит о 3 нм.

А где вообще Intel? Только что еле-еле переползли на 10 нм?

Мы решили узнать, что измеряют эти нанометры? И так ли важно ими мериться или это просто маркетинг? И реально ли Intel так безбожно устарел?

Прежде чем перейти к процессорам в наших смартфонах и компьютерах, немного основ как устроен процессор?

Знакомьтесь — это транзистор! Ключевой элемент всех процессоров. Фактически транзистор — это переключатель. Ток течет через него — это 1, ток не течет — это 0. Это и позволяет считать в двоичной системе — основа всех процессоров!

Раньше транзисторами были вакуумные лампочки. Условно — горит или не горит: единица или ноль.

Таких лампочек нужно было очень много, чтобы всё как-то работало. Например, компьютер ENIAC 1946 года, который участвовал в создании водородной бомбы насчитывал 17,5 тысяч вакуумных ламп и весил 27 Тонн, занимая 167 квадратных метров. При этом он жрал 150 кВт электричества.

И тут один из ключевых моментов, на который стоит обратить внимание. Еще раз повторю энергопотребление у этих 17,5 тысяч лампочек составляло 150 кВт.

Но в начале 1960-х случилась революция — изобретение и начало производства полевых транзисторов. Как раз у них исходным полупроводником является кремний — отсюда и всем известная силиконовая, кхм, то есть Кремниевая долина!

И тут понеслось! Размеры транзисторов уменьшились настолько, что они стали потреблять существенно меньше электричества и занимать меньше места. И количество транзисторов в вычислительной технике начало увеличиваться с огромной скоростью! А вместе с ним и мощность вычислительных систем!

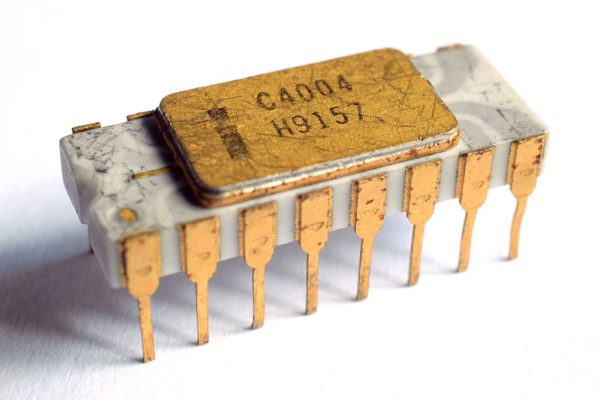

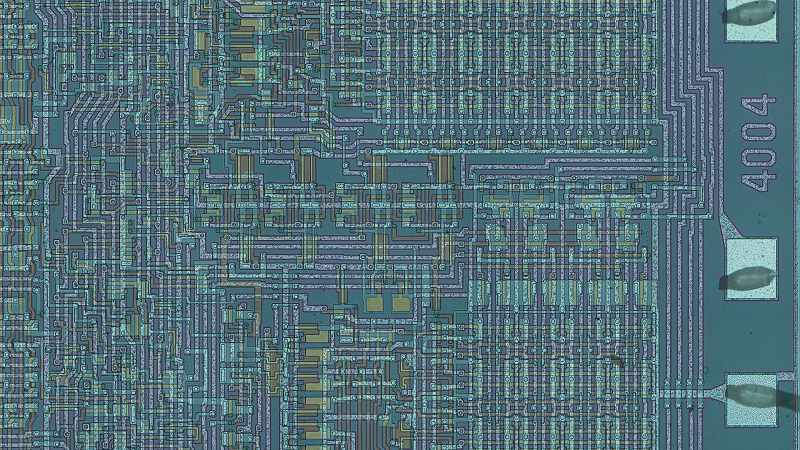

В первом промышленном процессоре Intel 4004, который был выпущен в 1971 году было 2250 транзисторов.

А сейчас например в A13 Bionic этих транзисторов 8.5 миллиардов — это больше чем людей на планете! Ну пока…

Но на сколько вообще уменьшились современные транзисторы, насколько они маленькие? Простое сравнение легкое для понимания — например, с человеческим волосом!

На его срезе можно разместить почти 1.5 миллиона современных транзисторов сделанных по 7-нанометровому техпроцессу!

То есть у вас на толщине человеческого волосе можно разместить в 4 раза больше транзисторов, чем было в процессоре Intel 4004!

Почему же надо уменьшать? Тут все более-менее очевидно!

Во-первых, чем меньше транзистор — тем меньше он потребляет энергии. Вы уже это поняли на примере ламповых.

А во-вторых — их больше помещается на кристалле, а значит растёт производительность. Двойная выгода!

И тут мы переходим к понятию техпроцесса или Technology Node — что же это такое?

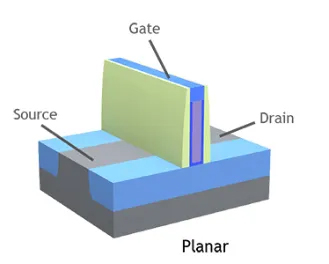

Если максимально упростить, то значением техпроцесса исторически являлась минимальная длина канала транзистора — как видно на картинке — не стоит его путать с размерами транзистора целиком.

То есть, чем меньше размер техпроцесса — тем лучше — это нам и пытаются донести компании, но так ли всё просто?

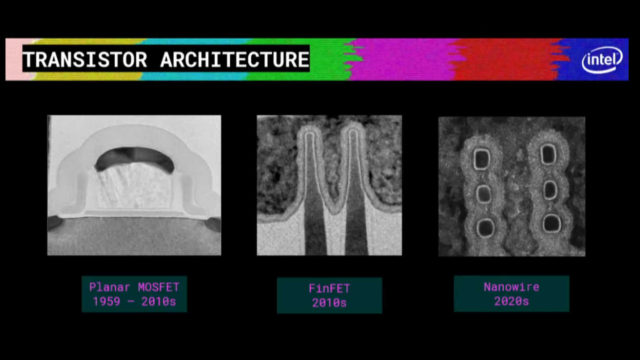

И тут важно другое: транзисторы бывают разные и они отличаются не только по размеру, но и по своей структуре.

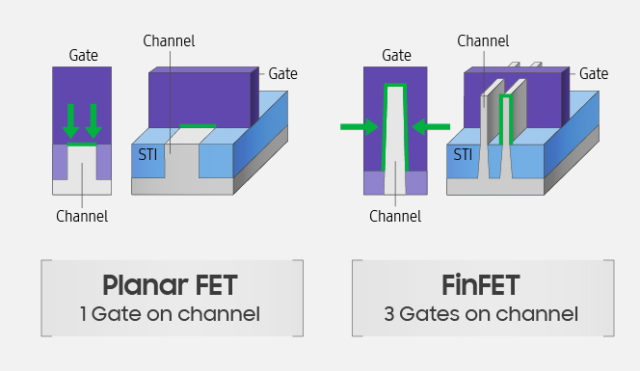

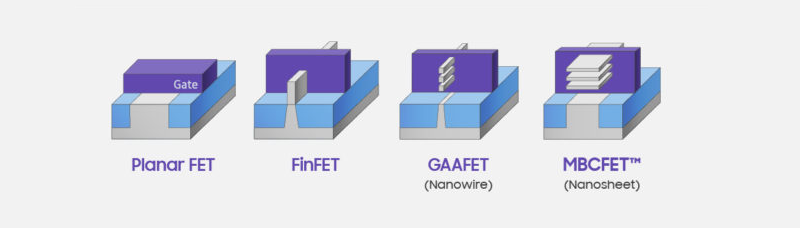

Классические, планарные или плоские, транзисторы перестали использоваться относительно недавно — в 2012 году. Они уступили место трёхмерным транзисторам, где вытянули канал в третье измерение, уменьшив его толщину и тем самым уменьшив сам транзистор. Такая структура называется FinFET — они и используются сейчас.

Данная технология очень помогла уменьшить размер транзисторов и главное — сильно повысила количество транзисторов на единицу площади, что и является одним из ключевых показателей для производительности!

Но означает ли сегодня понятие техпроцесс тоже самое, что и несколько лет назад?

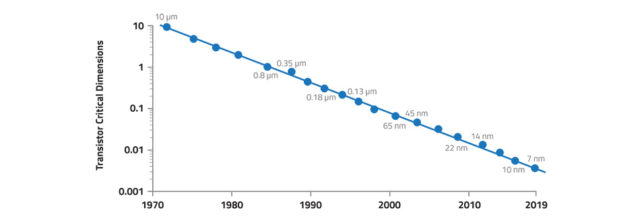

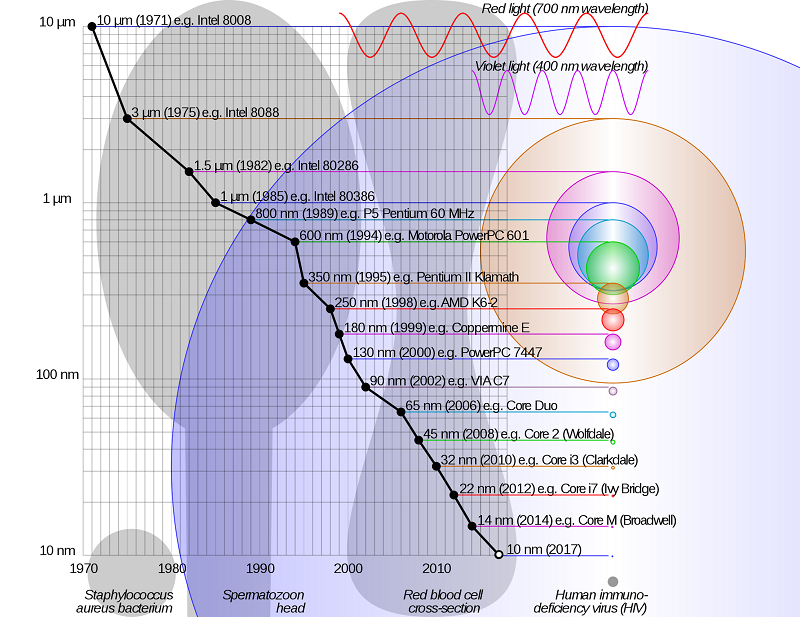

Во всей индустрии прослеживалась очень важная тенденция — каждый следующий техпроцесс был меньше предыдущего на 30%, что помогало удвоить количество транзисторов при сохранение того же энергопотребления — например 130*0.7=90 нм, 90*0.7=65 нм, далее до 45 нм, 32 нм, и так далее.

И это пока соответствует Закону Мура:

Количество транзисторов, размещаемых на кристалле интегральной схемы, удваивается каждые 24 месяца.

Что же стоит за этой игрой чисел?

Мы уже выяснили, что техпроцесс — это размер затвора транзистора, то есть длина канала, который пропускает или не пропускает через себя ток и этот размер ключевой!

Но оказывается это истинно, только если мы говорим о старых 32 нм — там все точно, хоть линейкой измеряй! И этот параметр был закреплен документально!

Но так было до 2009 года, когда из так называемого “Международного плана по развитию полупроводниковой технологии” было исключено понятие техпроцесса и его обозначения!

Простым языком — цифры указанные в тех процессе сегодня — это просто маркетинговый лейбл!

Производители пошли вразнос и начали называть всё подряд 10, 7 и вообще 5 нанометрами, а кто-то уже говорит и о 3 нанометрах! Можно всё это ставить в кавычки, как простое обозначение поколения процессоров!

Вот вам например структура процессора Apple A12, произведенного на заводе TSMC по 7- нанометровому техпроцессу. Обратите внимание на шкалу масштаба в левом нижнем углу.

Если сравнить масштаб и посчитать, то получается, что ширина канала — 8 нанометров, при том, что официально процесс называется 7-нанометровым.

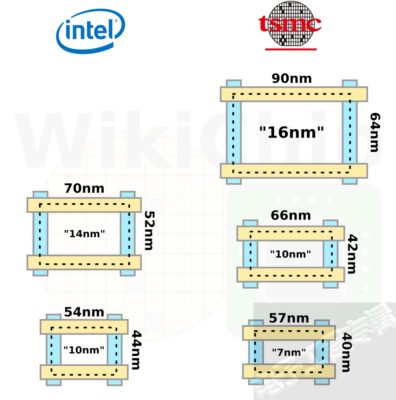

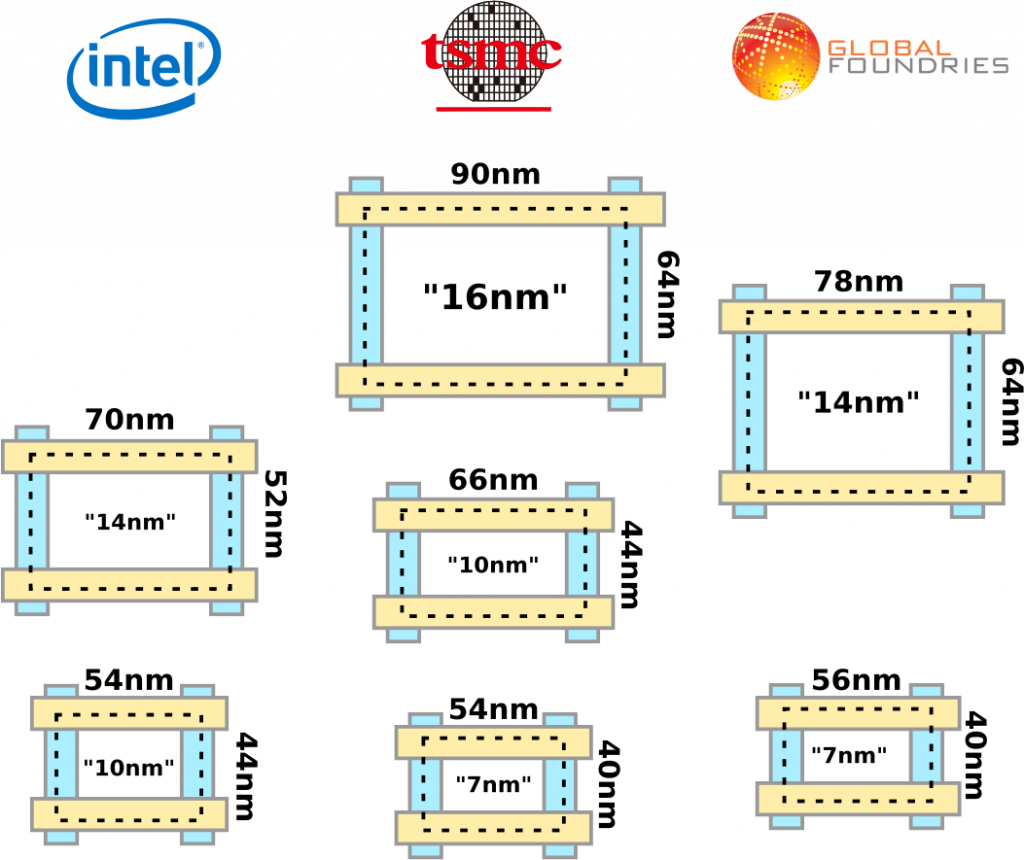

Теперь давайте сравним 10-нанометровый процесс у Intel и 7-нанометровый у TSMC.

Кстати, знайте, что сегодня TSMC это компания, которая производит процессоры для AMD, а также делает Apple A13 и Snapdragon 865 — поэтому считайте, что мы сравниваем сразу все их чипы.

Обратите внимание на размерность. Сразу видно, что те же 10нм у Intel почти такие же как 7 нанометров у TSMC! Так что выходит Intel не так уж отстали от AMD и других производителей — они просто проиграли маркетинговую битву? Тут тоже все не так однозначно!

Внезапно по некоторым параметрам Intel даже выигрывают у TSMC.

Смотрите на 1 квадратный миллиметр 10нм кристалла Intel помещается примерно на 5 процентов больше транзисторов, чем на 7нм у того же Apple, Qualcomm или AMD.

Но при этом у повышенной плотности есть и минусы — увеличенный нагрев!

Значит получается что кристаллы Intel мощнее, но за счет плотности они больше греются. Таким образом, мы получаем тот самый пресловутый троттлинг.

А процессоры производства TSMC — Apple Qualcomm и AMD выигрывают именно за счет более просторного расположения транзисторов примерно тех же размеров.

Как они это делают — это скорее вопрос внутренней архитектуры, а не циферка, которая стоит в названии тех процесса.

Не думайте, что я забыл про архитектуру N7FF+ — да она еще плотнее чем у Intel, но если говорить о чипах серия AMD Zen 2, Applу A13, Snapdragon 865 — все сделаны на основе TSMC 7FF и она проигрывает в плотности Intel.

Единственный процессор, который уже производится по новой технологии N7FF+ с использованием экстремальной УФ-литографии — это Kirin 990 5G. Тут конечно плотность транзисторов сильно возрастает — аж на 15 процентов!

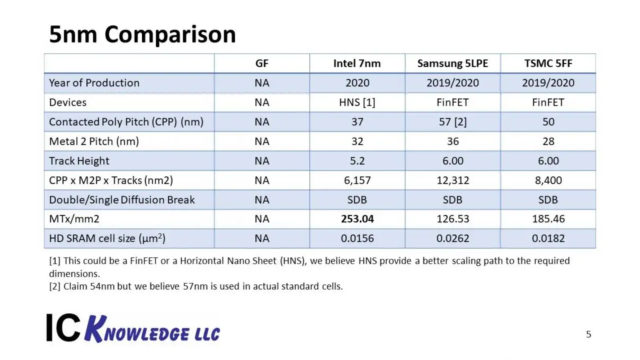

По идее производители просто идут по немного разному пути и если заглянуть в будущее, то становится понятно по какому: вот вам табличка того как все будет — чипы следующего поколения.

Нас интересует строчка про плотность транзисторов на 1 квадратный миллиметр!

По этим данным Intel более чем на 30 процентов обходит и Samsung, и TSMC в плотности транзисторов — и это при том, что тут мы сравниваем уже 7 нм у одного производителя и 5 у другого.

Откуда такой прирост? Как возможно такое повышение плотности — процы просто будут взрываться или работать только с навороченными система охлаждения?

Не совсем так. Все дело в том, что Intel планирует перейти на транзисторы совершенно другой структуры — под названием HNS — Horizontal Nano Sheets — это и позволит сделать скачок!

Но похожие планы есть и у Samsung — они идут немного в другую сторону к структуре Gate-All-Around FET.

Вот как это выглядит в реальности — не так симпатично, но вы только подумайте о том, какие они маленькие!

В итоге мы поняли, что за маркетинговыми названиями 7 нм и 5 нм скрывается битва архитектур, а в будущем мы сможем выяснить чей же путь был верным.

Что можно сказать абсолютно точно — нас ждёт огромный скачок среди всех чипов как мобильных так и десктопных уже в течение ближайших нескольких лет.

На этой ноте не хочется заканчивать тему процессоров, ведь мы изучили немало информации и документов, в том числе разобрались в процессе производства. Например, вы слышали о таком процессе Экстремальная Ультрафиолетовая Литография? Если на пальцах, это какая-то фантастика — капля олова превращается в плазму после попадания лазера: именно так создаются современные процессоры. Но сами установки может создавать только одна компания в мире и все гиганты от нее зависят.

Современные техпроцессы — грандиозный обман: разбираемся в маркетинговых тонкостях процессоров

Мы уже привыкли, что помимо ядер и частот многие производители указывают и даже хвастаются техпроцессом, по которому был произведен чип. Более того, эта величина считается лучше, если она меньше — редкость для «железа». Но что это такое, техпроцесс? Как он считается? Застряла ли Intel на самом деле на 14 нанометрах? Давайте разбираться.

Разумеется, без теории нам сегодня не обойтись. Итак, что же такое процессор? Грубо говоря, это скопление миллионов и миллиардов транзисторов, конденсаторов и резисторов в определенных комбинациях. Нам интересны только транзисторы — именно благодаря им наши процессоры могут выполнять вычисления.

Каким образом? Транзистор по сути — это переключатель. Если ток через него не течет, то это можно обозвать логическим нулем. Течет — единицей. Бинго, мы получили простейшую двоичную логику. И если у одного транзистора может быть только два состояния, то у двух — уже четыре, а у десяти — больше тысячи. Вот и получается, что современные CPU с миллиардами транзисторов позволяют обсчитывать все что угодно, начиная от физики в играх и заканчивая моделированием черных дыр.

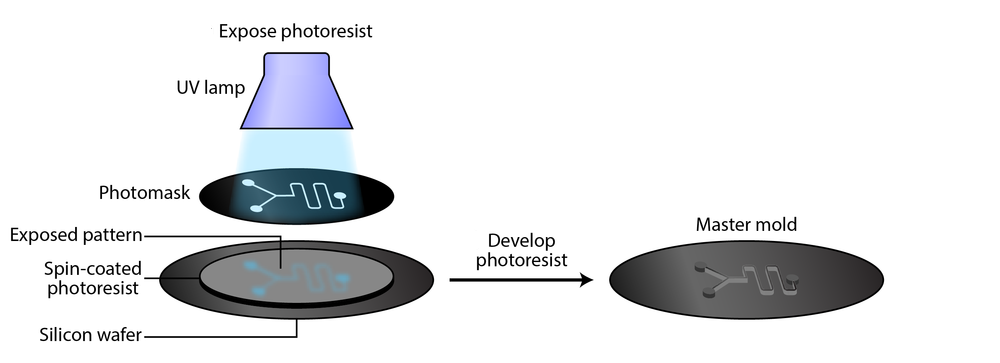

Но что-то мы отвлеклись. Итак, нам нужно создать транзисторы. Много транзисторов. Не вдаваясь глубоко в подробности, получаются они путем фотолитографии: свет определенной длины волны проходит через маску и оставляет на заготовке след, который собственно и является транзистором. На деле там все куда сложнее, но это уже тема для отдельной статьи.

И вот тут мы сталкиваемся с проблемой: разрешающая способность фотолитографического оборудования конечна — но, разумеется, постоянно увеличивается. Поэтому нужно было ввести параметр, который позволял бы сравнивать процессоры, созданные различными производителями на различном оборудовании.

Процесс фотолитографии.

Так и был введен техпроцесс. И нет, он показывает не размер транзистора, как многие думают. По сути он показывает технологический предел оборудования — то есть минимальный «штрих», который лазер через маску можно оставить на заготовке. И в случае с транзисторами он совпадал с самой тонкой их частью — затвором.

Логика тут проста: если у вас есть сверло на 10 мм, вы никак не сможете сделать дырку в 5 мм. А вот в 15 или 20 мм — без проблем. С фотолитографией все аналогично: если разрешающая способность вашего оборудования, допустим, 5 микрометров (5 мкм, 5000 нм), то вы не сможете сделать затвор транзистора меньше этой величины. А сам транзистор при этом, разумеется, будет в разы больше.

Почему такой параметр как техпроцесс важен? Да потому что он по сути показывает общую технологичность процессора: чем меньше техпроцесс, тем больше транзисторов можно поместить на той же площади — а, значит, тем быстрее будет работать процессор. Более того, чем меньше транзистор, тем меньше он требует энергии для работы и тем меньше выделяет тепла.

Разумеется, на заре создания процессоров никаких проблем с уменьшением техпроцесса не было: даже не меняя лазеры, которые изначально работали на длине волны в 700 нм (красный свет), можно было уменьшать сами маски, что позволило увеличить разрешающую способность оборудования — а, значит, уменьшить затворы транзисторов — более чем в 3 раза, с 10 до 3 мкм, всего за четыре года, с 1971 по 1975-ый.

Что интересно, так как техпроцесс в те годы был больше длины волны видимого света (сотни нанометров), то можно было в микроскоп разглядеть отдельные транзисторы, например, первого коммерческого процессора Intel 4004, который работал на частоте всего 500-740 кГц:

В дальнейшем пришлось перейти на фиолетовые лазеры (400 нанометров), продолжать играться с масками, но в общем и целом никаких проблем не было: к 1985 году была преодолена планка в 1 мкм, а начало нового тысячелетия мы встретили со 130-нм процессорами с частотой выше 1 ГГц, вмещающими в себя сотни миллионов транзисторов, которые в обычный микроскоп уже не разглядишь.

Я не просто так заострил внимание на 130 нанометрах — это был последний техпроцесс, который позволял сравнивать чипы различных компаний между собой и с предшественниками, чтобы оценить энергоэффективность и рост производительности.

Первый звоночек прозвучал в начале нулевых при переходе к якобы 90-нм техпроцессу. Да, это первый условный техпроцесс: 90 нм, которые мы можем встретить в Pentium 4, указывали уже не на разрешение фотолитографического оборудования, а на то, что площадь транзистора уменьшилась вдвое по сравнению с предыдущим 130-нм техпроцессом.

А раз площадь уменьшилась вдвое, то линейные размеры должны снизиться примерно в 1.4 раза. И если вы поделите 130 на 90, то столько и получите. И 90 при делении на 65 даст тоже самое, как и деление 65 на 45. Короче говоря, пошел откровенный «подгон» под закон Мура, который говорит нам о том, что число транзисторов на интегральной схеме удваивается раз в 2 года.

Иными словами, от абсолютно четкого параметра — затвора транзистора, который точно задает «качество» литографического оборудования — в начале нулевых производители перешли к линейным размерам транзисторов, что в общем и целом является достаточно размытым показателем, который слабо связан с затвором транзистора, что исказило саму суть техпроцесса.

В итоге ближе к концу нулевых мы получили грустную картину: вроде и AMD, и Intel производят свои процессоры на схожих техпроцессах в 45 и 40 нм, да вот только Core 2 Duo оказываются гораздо энергоэффективнее Athlon на схожих частотах, что лишний раз доказывает «маркетинговость» техпроцессов уже тогда.

Отказ от понятия «техпроцесс»

Глядя на все это безумие, инженеры, которые любят четкие физические величины, в рамках «Международного плана по развитию полупроводниковых технологий» взяли и вообще отказались от техпроцесса как от технологической переменной. Иными словами, начиная аж 2009 года указанные производителями техпроцессы — чисто маркетинг, нередко без всякой физической подоплеки.

Однако еще пару лет все продолжалось как и раньше — собственно, зачем менять то, что работает? Площади транзисторов все также получалось уменьшать, чтобы соответствовать закону Мура, поэтому производители продолжали делить старые техпроцессы на 1.4 и писать новые значения.

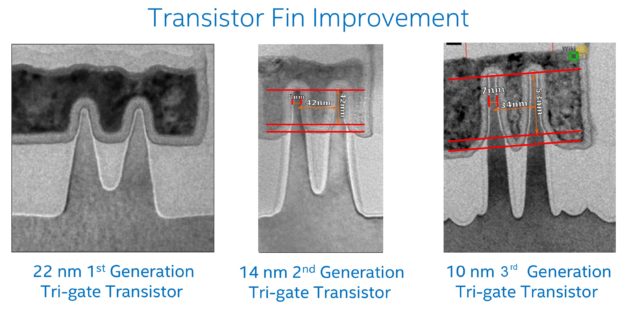

Второй звоночек прозвенел в начале 2010-ых: если 32-нм техпроцесс еще получилось сделать, то вот переход к 22 нм вовремя вызывал уже серьезные проблемы. Решением стал переход из 2D в 3D: если снижение размера затвора ниже

30 нм приводило к тому, что разрушался сам транзистор (он начинал пропускать ток тогда, когда не надо — через такую «узкую» преграду могли туннелировать электроны), то почему бы не сделать путь для электронов длиннее, выставив на их пути кремниевый гребень?

Так и родилась технология FinFET, что дословно переводится как «плавниковый полупроводниковый транзистор». Теперь вместо того, что бежать по прямой, электронам приходилось огибать гребень (зеленый путь на схеме ниже):

При этом, как можно заметить, физические размеры затвора транзистора не изменились, а раз теперь эффект туннелирования преодолен — можно продолжать уменьшать затвор и дальше, что все с радостью и продолжили делать.

Однако проблема в том, что это убивает определение техпроцесса. Насовсем. Все дело в том, что даже если фотолитографическое оборудование может создавать меньшие линейные затворы транзисторов, их все равно делают длиннее за счет трехмерного расположения, дабы не было туннелирования. И за счет 3D сам затвор и собственно транзистор оказываются меньше. То есть теперь техпроцесс совершенно не связан с разрешающей способностью оборудования.

Современные техпроцессы: маркетинг на маркетинге

В итоге такая путаница развязала руки маркетологам. Это наложилось в том числе и на то, что даже с ухищрениями типа FinFET мы с каждым годом все ближе к предельным возможностям кремния, и создавать более компактные транзисторы (и их затворы) становится все сложнее.

Как итог, сейчас техпроцессы компании считают так, как им удобнее. Кто-то продолжает по старинке считать занимаемую площадь (ага, трехмерного транзистора — ощутили достоверность?), кто-то считает техпроцесс по количеству транзисторов (ближе к правде, но все еще из-за трехмерной структуры не то) — короче говоря, я просто оставлю схему ниже:

Хорошо заметно, что 10-нм техпроцесс Intel на самом деле не так и плох, как его малюют: он ощутимо лучше 10-нм техпроцесса TSMC и даже по некоторым параметрам лучше тайваньских 7 нм! Так что Intel даже меньше лезет в маркетинг, чем TSMC.

Временами бывает еще забавнее: ниже показано сравнение затворов транзисторов у 14-нм процессоров Intel и 7-нм решений AMD (это опять TSMC). Хорошо видно, что разница минимальна, 24 против 22 нм. Иными словами, TSMC приукрашивает реальность аж в 3 раза!

Думаете это все? Да как бы не так: Intel планирует перейти от FinFET к HNS, Horizontal NanoSheets, горизонтальным нанолистам. Грубо говоря, это сравнимо с обработкой одним ядром сразу двух логических потоков — теперь в одном транзисторе «гребень» разделится на несколько частей:

Думаю, вы уже поняли, что заикаться про техпроцесс тут не имеет абсолютно никакого смысла. Понятно что производители нарисуют нам и 3 нм, и 2, и может даже меньше — никакой связи с физикой тут не будет и близко.

Итог — не верьте нанометрам

Что в результате? Аж 20 лет назад техпроцессы перестали привязываться к «железу». 10 лет назад техпроцесс вообще перестал быть физической величиной. Так что в будущем, когда на презентациях вам будут вещать о новых инновационных 3-нм процессорах — улыбнитесь и дождитесь тестов, которые точно расставят все точки над i.

5 нм против 3 нм

Промежуточные техпроцессы, разные типы транзисторов, и множество других вариантов добавляют неопределённости в процесс производства электроники

Производители электроники готовятся к следующей волне передовых техпроцессов, но их клиенты столкнутся с кучей сбивающих с толку вариантов – разрабатывать ли чипы по техпроцессу 5 нм, подождать 3 нм, или выбрать нечто среднее.

Путь к 5 нм хорошо определён, в отличие от 3 нм. После этого ландшафт становится запутанным, поскольку фабрики добавляют промежуточные техпроцессы, типа 6 нм и 4 нм. Переход на любые из этих техпроцессов весьма дорог, а преимущества не всегда очевидны.

Ещё один повод для беспокойства – сжимающаяся производственная база. В случае самых передовых техпроцессов выбор производителей оказывается невелик. В индустрии раньше было несколько ведущих производителей, но со временем эта область сузилась из-за резко возросшей стоимости и сокращения пользовательской базы. В целом, чем меньше производителей, тем меньше вариантов по технологиям и ценнику.

Сегодня Samsung и TSMC – два единственных производителя, работающих с техпроцессами 7 нм и ниже, хотя это может поменяться. Intel и китайская компания SMIC разрабатывают передовые техпроцессы. Intel, не самый крупный игрок в области коммерческого производства, испытывает проблемы с разработкой техпроцесса в 10 нм. И неясно, получится ли у SMIC выдать 7 нм, поскольку эта тема пока находится в стадии исследований и разработок (то же самое происходит у Intel с техпроцессом 10 нм).

Что касается более передовых техпроцессов, Samsung и TSMC работают с 7 нм, используя транзисторы finFET, и оба производителя собираются продолжать это и на 5 нм. В отличие от традиционных планарных транзисторов, finFET – это трёхмерные структуры, с лучшей производительностью и меньшими утечками.

Затем на 3 нм Samsung перейдёт от finFET к новой архитектуре транзисторов, нанослойным FET [nanosheet FET], представляющим собой развитие технологии finFET. TSMC пока не раскрывает своих планов на 3 нм, оставляя многих клиентов в подвешенном состоянии. TSMC, по информации источников, взвешивают разные возможности, включая нанослои, нанопровода и форсированные finFET. Intel, TSMC и другие также работают над новыми формами передовой упаковки в качестве возможных вариантов уменьшения масштаба.

Тем не менее, на 3 нм размере транзисторные технологии могут пойти в разных направлениях. finFET пока ещё могут сыграть, но этой технологии требуется сделать некоторые прорывы. Судя по всему, индустрии придётся готовиться к переходу на новую архитектуру 3 нм техпроцесса, и следующего промежуточного техпроцесса на 2 нм, судя по планам развития одной организации, работающей в этой области.

«5 нм – это всё ещё finFET, — сказал Наото Хоригучи, программный директор в Imec. – Допустим, что на 3 нм мы вступим в переходный период от finFET к другим архитектурам. Мы считаем, что это будут нанослои».

Нанослойные FET относятся к архитектуре транзисторов с круговым затвором (gate-all-around, GAA). И это не единственный из возможных вариантов. «Индустрия весьма консервативная. Её участники попытаются выжать из finFET всё до предела, — сказал Хоригучи. – На техпроцессе 3 нм у нас есть возможность использовать finFET. Но нам потребуется совершить несколько инноваций finFET, улучшить его в общем и целом».

Останутся ли производители чипов на техпроцессе 7 нм, мигрируют до 5 нм, 3 нм или до промежуточного? 7 нм обеспечивает достаточно производительности практически для всех применений, поэтому этот техпроцесс будет жить ещё долго. За его пределами существует несколько высокопроизводительных вариантов, и все они стоят дороже. И мы ещё посмотрим, успеют ли эти технологии появиться вовремя.

Рабочее напряжение разных техпроцессов – планарные транзисторы, finFET и нанослойные FET.

Разорение производств

Чип состоит из множества транзисторов, играющих роль переключателей. Много десятилетий прогресс интегральных схем соответствовал закону Мура, по которому плотность транзисторов на устройстве удваивается в срок от 18 до 24 месяцев.

В подобном ритме производители вводили новые техпроцессы с большей плотностью транзисторов, что позволяло индустрии снижать стоимость чипов в пересчёте на количество транзисторов. На каждом техпроцессе производители масштабировали спецификации транзисторов в 0,7 раз, позволяя индустрии увеличивать производительность на 40% при том же энергопотреблении и при двукратном уменьшении площади.

Индустрия интегральных схем следовала этой формуле и процветала. С 1980-х годов она прокладывала путь к быстрым ПК по снижающимся ценам.

К 2001 году существовало уже не менее 18 производителей с фабриками, где они могли производить чипы на 130 нм, что в то время было передовым техпроцессом, согласно IBS. Также тогда появлялось ещё несколько новых производителей, делавших чипы на заказ на чужих фабриках. Кроме того, практиковалось производство чипов для лабораторий, их разрабатывавших, но не имевших собственного производства.

К концу десятилетия стоимость производства и техпроцессы рванули ввысь. Не справившись с ростом цен, многие производители чипов перешли на модель fab lite. Они производили некоторые чипы у себя, а остальные отдавали на аутсорс.

Со временем всё меньше производителей чипов делали передовые устройства на собственных мощностях. Некоторые полностью избавились от производств или вышли из этого бизнеса.

Тем не менее, в 2000-х появилась бизнес-модель кремниевых мастерских. Мастерские отставали от Intel и других компаний по технологиям, но давали проектным компаниям доступ к различным процессам.

Следующее крупное изменение случилось на этапе в 20 нм, когда традиционные планарные транзисторы упёрлись в стенку и столкнулись с эффектом короткого канала. В ответ Intel в 2011 году перешла на транзисторную технологию следующего поколения, finFET, на 22 нм. Мастерские перешли на finFET на 16/14 нм.

У finFET есть несколько преимуществ по сравнению с планарными транзисторами. «В этой схеме весь транзистор вытягивается по вертикали так, что канал возвышается над подложкой, и вентиль обёртывается вокруг трёх сторон плавника. Увеличенная площадь контакта вентиля позволяет лучше контролировать ток утечки», — пишут Мэтт Когорно и Тошихико Мияшита из Applied Materials. Когорно – директор глобального менеджмента продукта, а Мияшита – главный технолог.

FinFET ещё и более сложные устройства, их сложнее производить и масштабировать на каждый следующий техпроцесс. В итоге, стоимость R&D выросли до небес. Так что теперь ритм полноценной смены техпроцесса вырос с 18 месяцев до 2,5 лет и более.

«Стоимость разработки сильно зависит от сложности SoC,- сказал Сэмюел Вэн, аналитик из Gartner. – Две трети уходят на разработку чипа. Остальное – разработка ПЛ, стоимость масок и улучшение выхода. Со временем стоимость проектирования тоже падает».

Тем не менее, тенденции цен изменили ландшафт мира интегральных микросхем. Со временем всё меньше компаний могут позволить себе оплачивать проектирование чипов для самых передовых техпроцессов. Многие из них полагаются в вопросах производства на мастерские.

Уменьшение количества клиентов вместе с ростом стоимости производства повлияли на ландшафт мастерских, производящих передовые чипы. К примеру, на рынке 16/14 нм осталось пять производителей/мастерских: GlobalFoundries, Intel, Samsung, TSMC и UMC. SMIC также работает с finFET на техпроцессе 14 нм.

А на 7 нм случился другой переход. Техпроцессы и стоимость производства продолжали расти, а прибыль на инвестиции была уже под вопросом. В итоге GlobalFoundries и UMC в прошлом году прекратили попытки разработать техпроцесс на 7 нм. Обе компании продолжают работать на рынке 16/14 нм.

Пытаясь развиваться дальше, Samsung и TSMC на полной скорости мчатся к рубежу 7 нм и за его пределы. После нескольких задержек, Intel планирует запустить производство на 10 нм в середине 2019 года, а на 7 гм – к 2021-му. SMIC тем временем не обещает никаких сроков.

Но не всем клиентам мастерских требуются передовые техпроцессы. Существует процветающий рынок для чипов на 28 нм. «Всё зависит от характеристик продукта, — сказал Вэн из Gartner. – Некоторым продуктам требуется максимальное быстродействие. Разработчики всё ещё могут использовать устаревшие техпроцессы. А чипы для применений, не требующих высокой производительности, могут жить и на техпроцессах N-1 и N-2».

Ему вторят другие. «Сколько компаний могут позволить себе новейший кремний сегодня с экономической точки зрения? Их количество уменьшается. На рынках, требующих чрезвычайно высокого быстродействия такая потребность будет всегда. Но в цепочке поставок, с точки зрения объёмов, в середине образуется разлом. Самым требовательным клиентам требуются техпроцессы на 7, 5, а возможно, когда-нибудь и 3 нм. Но все остальные немного притормозили», — сказал Уолтер Ын, вице-президент по бизнес-управлению в UMC.

Но в определённых случаях существует необходимость в самых передовых чипах – это серверы и смартфоны. Также появляется море новых стартапов, связанных с ИИ-чипами. Многие компании проектируют чипы для машинного обучения и глубокого обучения.

«Никто не спорит, что потребность считать что-либо в 10 раз быстрее, чем сегодня, всегда будет коммерчески полезной и конкурентоспособной, даже на не технических рынках. Тому свидетельством являются все эти уникальные достижения технологии глубокого обучения. Запросам на всё большую компьютерную мощность буквально не видно конца», — сказал Аки Фуджимура, директор D2S.

«Запросы на вычислительные мощности испытывали несколько крупных сдвигов – сначала это были GPU, а позднее – глубокое обучение, — сказал Фуджимура. – Глубокое обучение – это массивная технология поиска подходящих закономерностей, а обучение нейросетей – это задача последовательной оптимизации. Сейчас, когда мир придумал механизм обработки огромного количества данных и превращения их в полезную информацию в виде программы, способной к логическим умозаключениям, количество необходимых вычислений растёт вместе с количеством доступных данных. А поскольку количество данных во всех областях растёт в геометрической прогрессии, требования к вычислительным мощностям гарантированно значительно вырастут как минимум в области глубокого обучения».

Требуют ли чипы ИИ техпроцессов в 5 нм и дальше, остаётся неясным, но требования к увеличению вычислительных мощностей определённо существуют. Но миграция на эти техпроцессы не становится более лёгким или дешёвым процессом.

5 нм против 3 нм

Тем временем в начале 2018 TSMC достигла очередной вехи, став первым в мире производителем, задействовавшим техпроцесс на 7 нм. Позднее в гонку 7 нм включилась Samsung. Процесс изготовления чипов на 7 нм в основном базируется на finFET, и состоит из изготовления чипов с шагом затвора от 56 до 57 нм и минимальный шаг размещения металлических проводников [metal pitch] на 40 нм, согласно информации IC Knowledge and TEL.

В первой версии 7 нм TSMC использовала иммерсионную литографию на 193 нм и мультипаттеринг [multiple patterning]. В этом году TSMC обещает выпустить новую версию 7 нм с использованием экстремальной ультрафиолетовой литографии (EUV). EUV упрощает шаги техпроцесса, но это дорогая технология и у неё есть свой набор трудностей.

TSMC готовит свой новый техпроцесс на 5 нм к выходу в первой половине 2020 года. Новая технология от TSMC на 5 нм будет на 15% быстрее, чем 7 нм, и потреблять на 30% меньше энергии. Вторая версия техпроцесса 5 нм, выходящая в следующем году, будет на 7% быстрее. Обе версии будут использовать EUV.

TSMC уже набирает заказов на 5 нм. «Ожидается поступление крупных заказов от Apple, HiSilicon и Qualcomm, — сказал Хэндел Джонс, директор IBS. – Объёмы подложек составят 40 000 – 60 000 в месяц к четвёртому кварталу 2020».

Некоторые производители чипов хотят уйти от 7 нм, не тратя столько денег, сколько стоит 5 нм. Поэтому TSMC недавно представила новый промежуточный техпроцесс 6 нм, стоящий дешевле, но имеющий несколько компромиссов.

«Кажется, что числа N6 и N5 не отличаются, но на самом деле разрыв большой, — сказал С. С. Вей, директор TSMC на последнем совещании. – У N5, по сравнению с N7, логическая плотность увеличена на 80%. У N6 по сравнению с N7 всего на 18%. Как видно, существует большая разница между логической плотностью и эффективностью транзисторов. В итоге общее энергопотребление у чипа N5 ниже. У перехода на N5 есть много преимуществ. Но N5 – полноценный техпроцесс, и на разработку новых продуктов под него у клиентов уходит время. Прелесть N6 в том, что если у них уже есть проект под N7, то придётся потратить совсем мало усилий. Они могут перейти на N6 и получить определённые преимущества. И в зависимости от характеристик продукта и рынка, клиенты решат, что им делать».

Тем временем Samsung выкатила 5 нм, который появится в первой половине 2020. По сравнению с 7 нм, новый техпроцесс 5 нм от Samsung на finFET даёт до 25% уплотнения логики и на 20% меньше энергопотребления, или на 10% больше скорости работы.

Также Samsung представила новый промежуточный техпроцесс 6 нм, давая клиентам ещё один вариант. «У 6 нм есть преимущество масштабируемости с 7 нм и повторного использования интеллектуальной собственности», сказал Райан Ли, вице-президент по маркетингу мастерских Samsung. А в планах Samsung есть уже разработка техпроцесса finFET на 4 нм. Пока что по этой технологии практически нет открытой информации.

Samsung – единственная компания, объявившая о планах по разработке техпроцесса 3 нм. Для этого мастерская перейдёт на архитектуру транзисторов с круговым затвором, нанослои. TSMC пока не раскрывает планов, из-за чего некоторые полагают, что компания отстаёт. «На 3 нм у Samsung высокая вероятность выйти на объёмное производство в 2021 году, — сказал Джонс. – TSMC ускоряет разработку, пытаясь угнаться за Samsung».

На 3 нм TSMC изучает нанослойные FET, нанопроводные FET и даже finFET. Один из способов расширения технологии finFET – использование в каналах материалов с высокой подвижностью, а именно германия. Сегодняшние finFET устройства используют кремний или кремний-германий (SiGe) в каналах. Увеличивая примесь германия, можно увеличить подвижность канала – то есть, скорость прохода электронов по устройству. И тут проблемой является контроль дефектов.

Расширение технологии finFET имеет смысл. finFET на 3 нм обеспечивает путь перехода от 5 нм. Однако тут есть свои проблемы. Теоретически технология finFET упирается в тупик, когда ширина плавника достигает 5 нм, что близко к текущему состоянию. «Сегодня мы используем по два плавника для NMOS и по три для PMOS в стандартной ячейке, — сказал Хоригучи из Imec. – Один из важных аспектов 3 нм в том, что нам нужно перейти на архитектуру с одним плавником для стандартных схем ячеек. Единственный плавник должен достаточно хорошо работать. Чтобы расширить технологию finFET до N3, нужна особая технология улучшения мощности единственного плавника и уменьшения фоновых паразитных явлений».

Кроме высокой мобильности finFET, следующий вариант – это GAA. В 2017 Samsung представила Multi Bridge Channel FET (MBCFET) для 3 нм. MBCFET – нанослойный FET. Пробная партия MBCFET от Samsung появится в 2020.

У нанослойных чипов есть преимущества перед finFET. У finFET затвор загибается вокруг плавника с трёх сторон. В нанослоях затвор находится с четырёх сторон плавника, что даёт больше контроля над током.

По сравнению с 5 нм, нанослойные FET от Samsung обеспечивают увеличение эффективности логической области до 45% и уменьшение энергопотребления на 50% или увеличение быстродействия на 35%. «У структуры finFET есть свои ограничения по масштабируемости, поскольку напряжение питания нельзя опускать ниже 0,75 В. Наша инновация с использованием нанослоёв позволяет уменьшить напряжение до значений менее 0,7 В», — сказал Ли из Samsung.

Технологий GAA бывает несколько видов, включая нанослойные FET и нанопроводные FET. Сам по себе GAA – следующий шаг после finFET. В этой системе finFET располагается на боку, а потом разделяется на горизонтальные кусочки. Кусочки формируют каналы. Материал затвора оборачивается вокруг каждого слоя.

По сравнению с нанопроводным FET, у такой схемы каналы шире, то есть, выше производительность и ток возбуждения. «У нанослоёв больше эффективная ширина, — сказал Хоригучи из Imec. – Нанопровода гораздо лучше справляются с электростатикой. Но их поперечное сечение очень мало. Это не даст преимуществ в вопросе эффективной ширины канала».

У архитектур GAA есть несколько проблем. Обычно они дают крайне небольшой прирост по сравнению с finFET на 5 нм. Производить чипы по этой технологии довольно тяжело.

«Следующее поколение GAA на 3 нм и ниже добавляет очередной порядок сложности в производство, — сказал Ричард Готшо, вице-президент и технический директор Lam Research. – На первый взгляд, она выглядит, как модификация finFET. Однако требования усиливаются, и сложность этой архитектуры GAA значительно выше, чем у finFET».

В процессе производства нанослойных чипов первый шаг – размещение тонких чередующихся слоёв SiGe и кремния на подложке. «У нас получается стопка кремний, кремний-германий, кремний. Мы называем это сверхрешёткой», — сказал в недавнем интервью Намсун Ким, главный директор инженерного управления Applied Materials. «Имея германиевое содержимое, необходимо обеспечить ему хороший слой изоляции».

Как минимум, пачка должна состоять из трёх слоёв SiGe и трёх кремния. Затем на пачку наносятся крохотные листовые структуры. После этого формируется изоляция с канавками, а потом – внутренние разделители.

Затем слои SiGe удаляются из сверхрешётки, оставляя кремниевые слои с пустым пространством между ними. Каждый кремниевый слой формирует основание листа или канала в устройстве. Затем необходимо нанести материал с высокой диэлектрической проницаемостью для создания затвора. «Между нанопроводами минимальное расстояние. Очень маленькое. Проблема в том, чтобы поместить туда металл рабочей толщины», — сказал Ким.

Индустрия годами работала над созданием технологии GAA, однако всё ещё остаются определённые проблемы. «Одна из главных – паразитная ёмкость, — сказал Ким. – Если вы спросите меня, каковы главные проблемы технологии GAA, то их две. Внутренние разделители и изоляция подложки».

Что дальше?

Насколько хватит технологии GAA или нанослоёв? «Нанослои проживут два-три следующих техпроцесса. Мастерские могут изготовить нанослои на N3. Следующее поколение так уж точно. А после этого, возможно, придётся изменить интеграцию нанослоёв или архитектуру. Но это всё равно будет архитектура нанослоёв», — сказал Хоригучи из Imec.

Индустрия исследует способы улучшения технологий GAA и finFET на передовых техпроцессах. В данный момент устройства с GAA дают небольшое преимущество по сравнению с finFET. К примеру, у предыдущего нанослойного чипа от Imec шаг затвора составлял 42 нм, а минимальный шаг размещения металлических проводников – 21 нм. Для сравнения, у finFET на 5 нм может быть шаг затвора в 48 нм и минимальный шаг размещения металлических проводников в 28 нм.

В лаборатории Imec продемонстрировала масштабируемость устройства на полупроводниках p-типа с двойной стопкой GAA и германием в канале. Используя схему без расширений, Imec разработала нанопровод с длиной затвора порядка 25 нм. Его можно приспособить и для нанослоёв. Как и у предыдущей версии, размер проводов составляет 9 нм.

Германий может сыграть роль в продолжении использования finFET за пределами техпроцесса в 5 нм. Imec продемонстрировала Ge nFinFET с рекордно высокими показателями Gmsat/SSsat и PBTI. Они были достигнуты благодаря улучшению замены материала с высокой диэлектрической проницаемостью.

Мы ещё увидим, удастся ли расширить технологию finFET до 3 нм. Также непонятно, появятся ли нанослойные чипы вовремя. В этом меняющемся ландшафте множество неизвестных и неопределённостей, и не существует графика прояснения ситуации.